Machineboy空

CPU 성능 향상 ③ 명령어 집합 구조, CISC와 RISC 본문

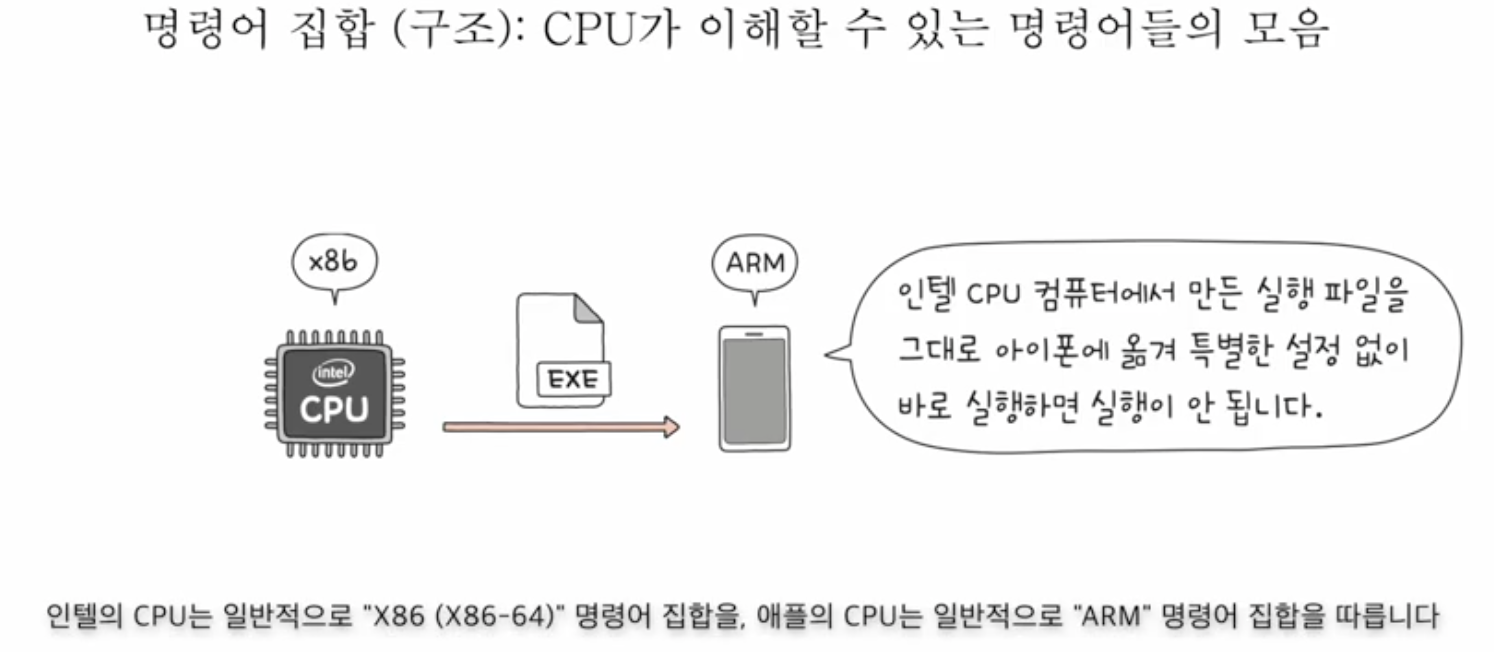

CPU는 다양하기 때문에 명령어의 세세한 생김새, 연산, 주소 지정 방식 등은 CPU마다 다르다

CPU들은 명령어 집합에 속한 명령어들만 이해할 수 있다

즉, 같은 코드를 컴파일할지라도 다른 어셈블리어가 도출된다.

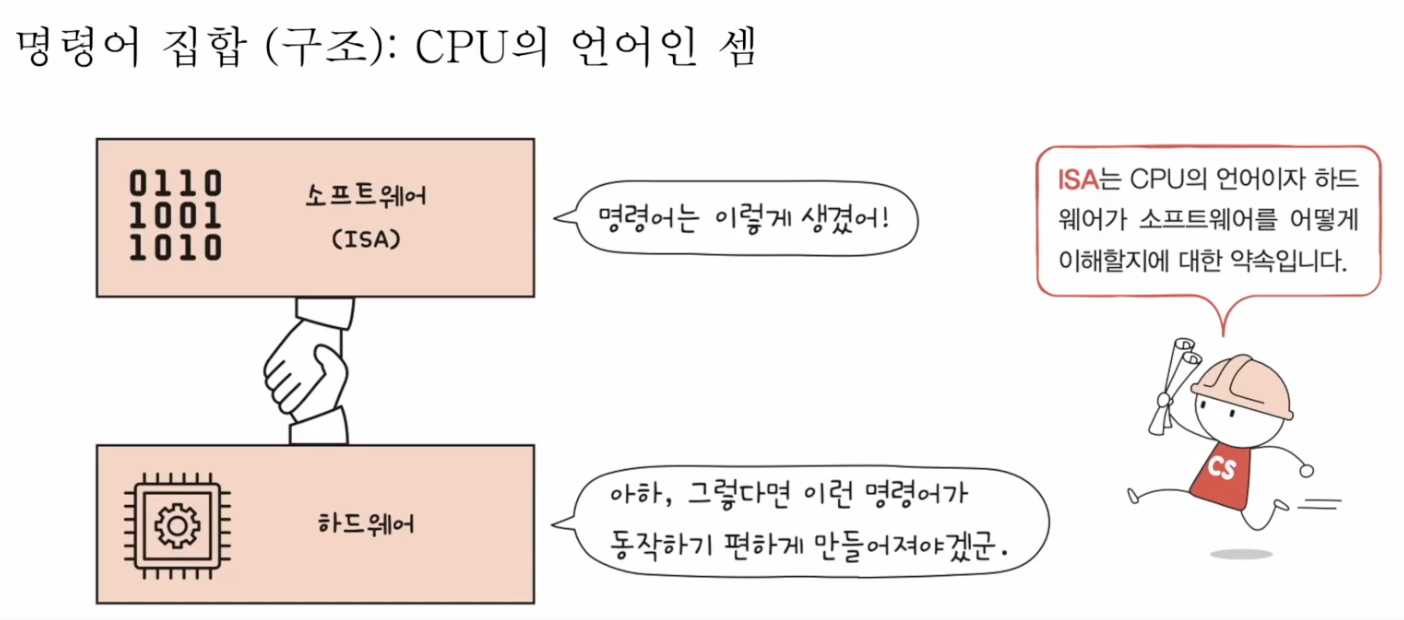

명령어 집합(구조) : ISA, Instruction set architecture

CPU의 언어인 셈.

언어에 따라 생활 양식 문화도 다른 것처럼,

명령어의 집합, 즉 CPU의 언어가 달라지면 명령어 해석 방식, 레지스터의 종류와 개수, 파이프라이닝의 용이성 등이 달라진다.

그래서 명령어 구조라고도 부르는 것

즉 명령어가 달라지만 그걸 좀 더 효율적으로 다룰 수 있는 하드웨어의 구조도 달라지기 때문에

ISA는 하드웨어가 소프트웨어를 어떻게 이해할지에 대한 약속이다.

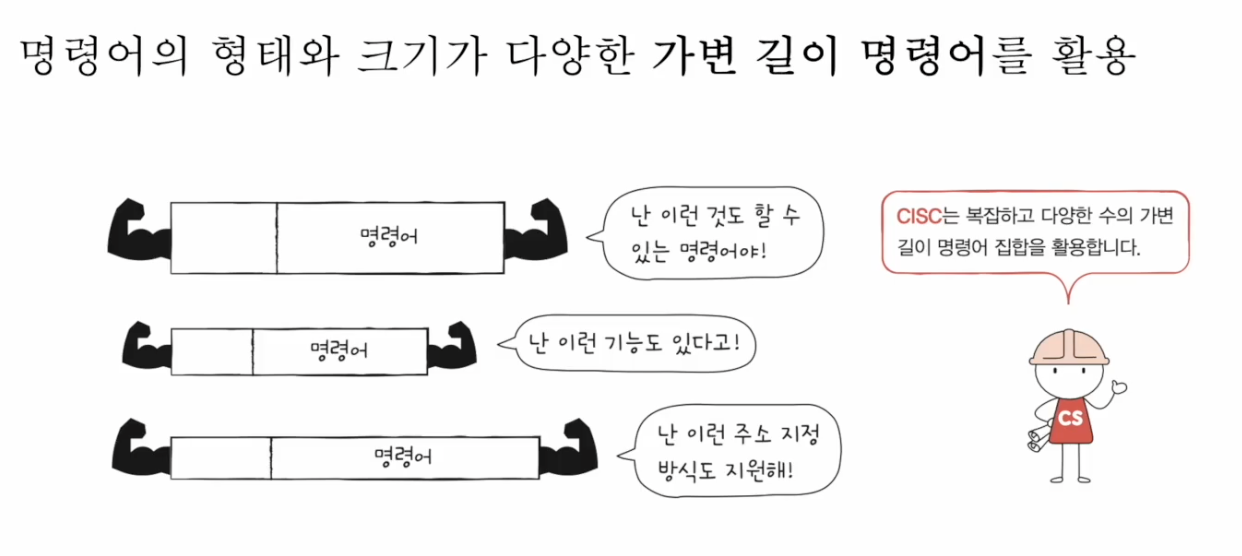

명령어 집합의 두 축 : CISC & RISC

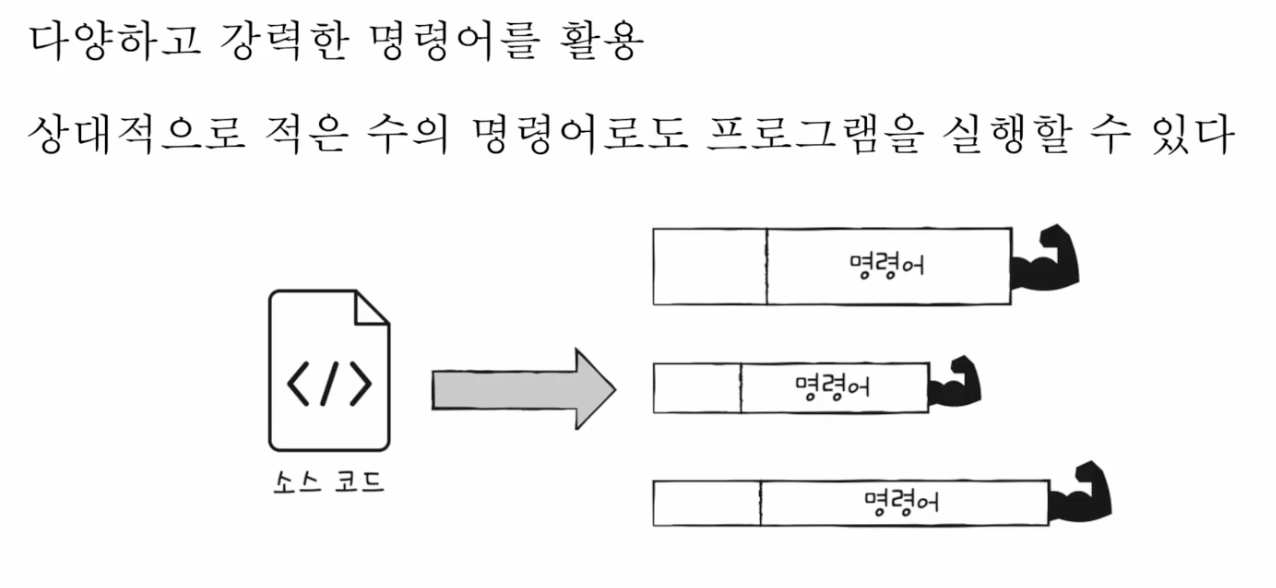

| CISC(Complex Instruction Set Computer) | RISC(Reduced Instruction Set Computer) |

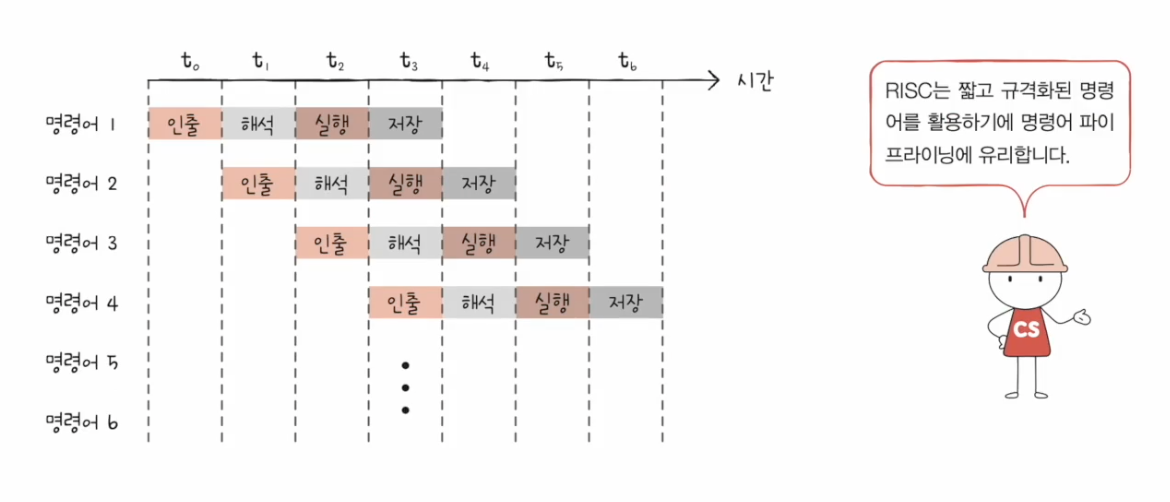

| 복잡한 명령어 집합을 활용하는 컴퓨터(CPU) | 명령어의 종류가 적고, 짧고 규격화된 명령어 사용 |

| CISC 기반 명령어 집합 구조 x86, x86-64 |

RISC 기반 명령어 집합 구조 arm |

|

가급적 1클럭 내로 실행할 수 있는 것으로 사용 |

메모리 주소 지정 방식도 다양하다 |

메모리 접근 최소화(load, store)하고 대신에 레지스터 십분 활용 |

파이프라이닝이 잘 되려면 일정한 것이 좋음, 하지만 명령어 하나하나 당 실행 시간이 들쭉날쭉하면 어려움 |

|

|

|

CISC가 실제로 실행될 때는 CPU 내부단위 마이크로 명령어 등 으로 잘게 쪼개서 실행됨

'Computer > CS' 카테고리의 다른 글

| 메모리 ② 메모리의 주소 공간 - 논리 주소, 물리 주소 (2) | 2024.01.08 |

|---|---|

| 메모리 ① RAM의 특징과 종류 - DRAM 과 SRAM (1) | 2024.01.08 |

| CPU 성능 향상 ② 명령어 병렬 처리 기법 - 명령어 파이프라인(Instruction Pipeline), 슈퍼스칼라(Superscalar), 비순차적 명령어 처리(OOOE) (2) | 2024.01.05 |

| CPU 성능 향상 ① 빠른 CPU를 위한 설계 기법 - 클럭(clock), 코어(core), 스레드(thread) (0) | 2024.01.05 |

| CPU ③ 명령어 사이클과 인터럽트 (1) | 2024.01.05 |